どうやら復旧したっぽいけれども、システムの脆弱性を示す話。こうした社会インフラ化したシステムは、障害を起こしにくく、万が一障害が発生した場合でも短時間で復旧可能にして欲しいものだ。

全銀ネットのシステム障害、復旧作業が完了

2023/10/12 09:06

全国銀行資金決済ネットワーク(全銀ネット)は12日、三菱UFJ銀行など10金融機関で発生した送金障害の復旧作業が完了したと発表した。12日午前8時半からのコアタイムシステムの時間帯から、他行宛ての振り込みが通常通り利用できるようになる見通し。

産経新聞より

復旧には2日間の時間を要したんだけど、結構な被害もあったみたいだから。

このブログでは珍しい話題だけれども、偶にはこんなのも良いかな。

堅牢で古いシステムの障害

全銀システムとは

余り聞かない名前のシステムだなと思っていたんだけれども、一般人もかなりお世話になっているシステムのようだ。稼働開始は1973年だそうな。

全銀システムとは、全国銀行データ通信システムといい、全国銀行内国為替制度に加盟する銀行間の内国為替取引に関する通知の送受信、および当該取引によって生じる銀行間の為替決済額の算出・清算などを集中的に行うオンラインシステムのことである。

つまり、一般人が関係してくる話としては、銀行間で送金をする時に使われるシステムってことだね。

全銀システムは、平日日中の内国為替取引に対応する「コアタイムシステム」と、平日夜間・土日祝日の内国為替取引に対応する「モアタイムシステム」によって構成されていて、平日夜間や土日祝日においても銀行への即時入金が可能となる。でも、24時間365日稼働するシステムってことになるので、トラブルが起きればなかなかメンテナンスも難しい。

500万件の取引に影響

で、今回は、10月10日の午前8時頃からトラブルが発生したようだ。

全銀ネット 不具合で振り込み140万件に影響 別の手段で対応へ

2023年10月10日 21時18分

金融機関どうしの資金のやり取りを担う全銀ネット=「全国銀行資金決済ネットワーク」のシステムに不具合が発生し、10日朝から11の金融機関で他行宛ての振り込みができない事態となりました。復旧の見通しは立っておらず、現時点で140万件の振り込みに影響が出ているということですが、11日の取り引きについては、別の手段で対応して振り込みができるようにするとしています。

全国銀行協会によりますと、10日午前8時半ごろ、一般社団法人の全銀ネット=「全国銀行資金決済ネットワーク」が運営する通称・全銀システムに不具合が発生しているのが確認されました。

NHKニュースより

1973年に稼働を始めた全銀システムは、日本の金融取引の基盤を支えてきたため、いきなり銀行振り込みができないと言われても困ってしまう。

全銀システム障害、2日で約500万件の取引に影響 12日朝の復旧目指す

2023年10月11日午後 7:37 GMT+9

全国銀行資金決済ネットワーク(全銀ネット)は、全国銀行データ通信システム(全銀システム)の不具合が、11日も解消に至らなかったと明らかにした。影響が出ている11の金融機関から他行への振り込み、他行から影響を受けた金融機関への振り込みを合わせて2日間で約500万件の取引に遅延や未処理などの影響が出ている。

ロイターより

日本経済に大きな影響が出たよね。

決済が出来ずに不渡り?!

被害状況はハッキリ伝えられていないが、不渡りになった手形や小切手というのもあっただろうとは思われる。

全国銀行協会は11日、今回の障害で手形・小切手等の決済口座に対する振り込みができないことにより不渡りとなった手形・小切手については、不渡報告への掲載の猶予を実施することを電子交換所参加銀行宛に通知した。

ロイターより

自転車操業している企業にとっては、なかなか死活問題だろう。

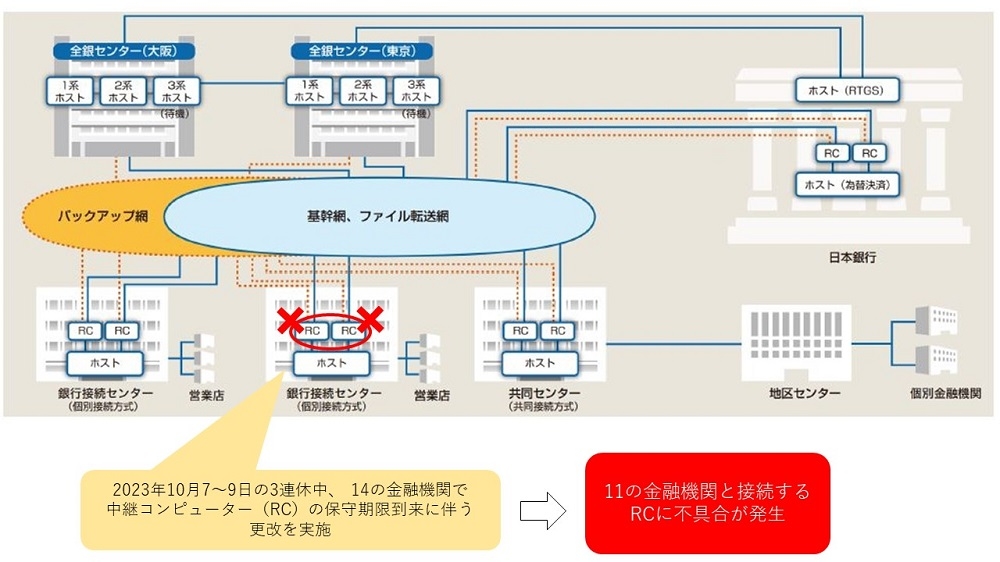

全銀システムの大規模障害、中継コンピューター2台ともに不具合で冗長構成が機能せず

2023.10.11

2023年10月10日午前8時30分ごろに発生した「全国銀行データ通信システム(全銀システム)」の障害。全国銀行資金決済ネットワーク(全銀ネット)は復旧に向けた対応を実施しているが、11日午前11時時点で解消のめどは立っていない。

全銀システムは東京と大阪の2カ所のセンターで並行運転し、システムを構成する各種装置や通信回線などをすべて二重化してある。顧客に影響が出るシステム障害が発生するのは1973年の稼働以降、50年間で初めてとなる。

日経XTECHより

そうならないように、システムの二重化が為されていたのにこの障害である。

中継コンピュータ(RC)が二重化されていたのに、2台とも不具合が生じたとのこと。……2台とも?

コアタイムシステムのRCを更改した14の金融機関のうち、11の金融機関で不具合が発生した。コアタイムシステムのRCは各金融機関に2台ずつ設置されていたが、2台とも不具合が生じ、冗長構成がうまく機能しなかった。全銀ネットは10日午前9時30分ごろ、ベンダーのNTTデータとの協議を経てRCのシステムをリブートしたが、不具合は解消しなかったという。

日経XTECHより

システムを二重化して、両方とも更改しちゃったってことか?そんな、まさか。

官房長官はサイバー攻撃の可能性を否定

ちなみにこれ、サイバー攻撃の可能性も疑われたのだけれど、これは政府によって「可能性は低い」と否定されている。

全銀システムの障害、サイバー攻撃による可能性低い=官房長官

2023年10月11日午後 4:43 GMT+9

松野博一官房長官は11日午後の会見で、全国銀行データ通信システム(全銀システム)の障害はサイバー攻撃による可能性は低いとの報告を受けていると述べた。

松野官房長官は、全国銀行資金決済ネットワーク(全銀ネット)から金融庁への報告に言及し「システム障害の原因はサイバー攻撃による可能性は低く、前週末に実施された全銀システムと金融機関をつなぐシステムを更改したことに伴う不具合と考えられると聞いている」と述べた。

ロイターより

原因がハッキリしていれば、対策は出来るのだろうし、サイバー攻撃の可能性も「低い」と言えるんだろう。

しかし、このシステムが人質に取られるようなことになると結構おおごとになりかねない。

古いシステムでもあるので、堅牢であることは誇るべき点もあるんだろうけど、新しい時代に対応することも考えるべきかも知れない。新しいことが全て良いとは言わないけれども、金融工学は随分と変革しているし、銀行業の規制をしている国は世界的に見ると多くない。そして、銀行を介さない金融取引も増えてきていて、結果的に銀行業の存続がちょっと怪しくなっている問題もあるので、考え直す良い機会かもね。銀行が苦しいのは、日本の超低金利政策が続いているからなんだけども。

追記

メモリ、不足だと?

全銀ネット障害、メモリー不足が要因 事前テスト甘く

2023年10月16日 19:30

三菱UFJ銀行など10金融機関で約250万件の送金が滞った全国銀行データ通信システム(全銀システム)の障害は、各金融機関と同システムをつなぐ機器の容量(メモリー)不足が要因だったことがわかった。機器の更新で処理量が増え、想定の容量を超えてパンクした。事前のテストが不十分だった可能性もあり、検証が求められる。

日本経済新聞より

想定ではいける計算だったけど、実際に接続してみたら思った以上に情報量が多かったという事なんだろうか。そんなアホな……。

OSが32bitから64bitに変更されたら、単位時間当たりの情報処理能力が上がってしまって、メモリの容量が足りなく……、いやそんなPCみたいな話はないかな。そもそも、メモリが足りなければ仮想領域で処理する話になるだけだし。よく分からない話だ。

ともあれ、事前検証が難しい事かも知れないけれど、システム設計時点である程度は分かりそうなものだけどなぁ。

まあ、原因が分かってヨカッタネ、ということなのだろうか。2日で巨額の損失が生じてしまったことを考えると、「事前テストが不十分でした」で終わる話では無いような気もするが。

コメント

原因はUpdateの失敗だそうです、Systemtestしていなかった。

未だ詳しい情報出ていませんが、アップデート問題だったことは記事でも触れています。

テストしていなかった……。していてこれじゃないかな?という気はしますが。

本来こっちへのコメント期待されてる身かもしれませんが、すみません大した情報は。。。。

これは、もう部品入手もメンテも困難なIBM360互換メインフレームコンピュータから現代的なコンピューター:WS,PCサーバー等への入れ替えの、念のために数段階にわけた(それでも非常に大掛かり)アップデートの第x番目の行程で起きた不具合と言うことのようです。

このブログお馴染みの話題で例えるなら、保守部品入手が困難になってきたF-2をF-35やGCAPに更新するまでの繋ぎとして、F-15EX相当への改修、たたしnステップ掛かるx段階みたいなハナシ。

基本:ザ・インターネットには接続しないクローズドネットワークだからサイバー攻撃の心配は少ないのかな? ただ回線工夫しないとEMP物理攻撃には脆弱かも知れない。

いえいえ、いつも参考になる情報をありがとうございます。

しかし、定期的に入れ替えているでしょうから、メインフレームは骨董品で設計されているわけですから、更新と言っても一筋縄ではいかない可能性も考えておくべきでした。流石に、導入当初のサーバーマシン使っていませんよね?

この辺りは分かったらまた追記したいと思います。

こんばんは!

>流石に、導入当初のサーバーマシン使っていませんよね?

ご懸念に従って少し調べた結果ですが、メインフレーム・コンピューター自体は今でも富士通が作っているが、2030年撤退・保障年限が意外と短く2035年ということらしいです。

そして非常に大規模・複雑システムなので、WS,PCサーバーに移行しても数年~? は、バグ対応のバックアップが要る。それを 2035年までに出し切って対策する必要がある。ための、タイトなスケジュールのようですね。

「富士通メインフレーム」

BOOK推定ですが、今や大企業としてのノブレス・オブリージュ的な使命感で作り続けているコンピューターで殆ど儲けはない。 そしてメインのCPUやI/Oプロセッサ (後者はPCより数千倍は強力)もFPGAベースしかないのかな?

で、WS,PCサーバーへの移行には、そもそもアーキテクチャの根本が異なるコンピューター間の移行なので、ソフトも大幅な書き換え、新規作成に、、近い、、と言うより互換性保証を考えると新規作成より手間は大変な作業ですね。

今回の不具合は、、、、ある意味仕方ない、、、だけど連休後の5・10日に持ってくるなよ! というマネジメント上の不手際が糾弾されているらしいです。

(ソース:スラド&5ch,,,、信ぴょう性は、記述内容から判断するしかない! (笑)

長い蛇足

【FPGA(フィールド・プログラマブル・ゲート・アレイ)】

先にGA(ゲート・アレイ)を説明しないと多分、分かんないですね。

「GA (Gate Array)」

文字通り、論理ゲート(トランジスタ)を、単にタテ・ヨコ1万×1万=10億個ほど並べた「だけ」のマスタスライスICを半導体メーカーが在庫し、顧客が各トランジスタをどう繋げるか決定した後、配線工程に流して完成させるIC。ASIC(application specific integrated circuit)の代表的な形態です。

ASIC≒セミカスタムICとしては最高性能を出せるので今でも多く使われています。

ただ、欠点として「最先端のCPU・GPU」相当品だと、配線だけで50~100層オーバーし、半導体製造工程は、まあ 1層≒1日なので、設計投入後モノが出てくるまで最速3カ月ほどかかります。

配線にバグ発覚し修正しても修正品が出てくるのが最短次の3か月後、、まあ1次設計後のバグ取りに下手すりゃ1-2年かかる。少量生産ではやってられない。

FPGA(Field Programmable Gate Array)

ICを基板にはんだ付け後、ユーザーがIC内部の配線を決定できるGA(GateArray)。仕組みとしては、上記GA(GateArray)の「あり得そうな配線」が全て配線済みで、その代わり「あり得そうな配線」は途中に「ON/OFFスイッチ」が設けてある。

黎明期はROMライターの親分みたいな専用装置でIC内部のマイクロ・ナノ・ヒューズを溶断したりして「ON/OFFスイッチのON/OFF」を決定してました。

しかしよく考えると「デジタルIC内部のON/OFF」てのは「メモリーに書き込んだ結果」と等価なのです。

そこで現在のFPGAは起動時に「コンフィグレーション」モードでメモリー書込み≒ON/OFF決定≒配線し、そこから使う方法が主流。

FPGAのメリット。

GAで数カ月かかった配線工程が一瞬で終わる。バグ取も一瞬。

欠点。ON/OFFメモリ分ICの規模が膨らむ。上記1万×1万=10億個のGAと同等規模のFPGAだと、ざっと60~80億個トランジスタの大規模ICとなる。

まあ、だけど極端な話「製品出荷後に明らかになった【ハードウエア・バグ】さえも、ソフトウェアの如くアップデート修正可能なため、高度なインテリジェンス製品への採用はどんどん増えている。

丁寧にありがとうございました。

確かに、富士通辺りは儲け度外視でやっているんでしょうね。信頼の維持もあるでしょうから。

FPGAの話は興味深く読ませて頂きました。

以前もコメントで説明頂いたと記憶していますが、どこでだったかなー。ただ、FPGAベースでやるとなると結構時間がかかるのでは?という気がしました。なかなかシステム的に長期間止められないシステムというのが、何とも面倒な話ですよね。

木霊様 こんばんは!

いつも私の蛇足まで丁寧に読んで返事まで頂きありがとうございます。

せっかくですので^^;

>FPGAベースでやるとなると結構時間がかかるのでは?

確かに全部イチからやると、結局CPU開発と同じになっちゃいますね。でも恐らくですが機能向上より互換性重視だろうメインフレーム開発だと「既存設計」を活かせてFPGAの方が便利って感じじゃないかな?

IC設計はトランジスタ100万個時代ぐらいまでは回路図書いてやってた(!)らしいですが、今は

「ハードウェア記述言語」で行い、

結構ソフトウエア開発に近い。 ソースプログラムの数十行が、機械語数十万個に変換されるイメージですね。

そして特に大きな機能アップじゃないメインフレーム開発なら、5Vロジック→3.3Vロジック(要するに時代にあった修理可能ロジック)への置き換え。だと、例えばWindowsX 用 Excelを WindowY用に書き換えてクロスコンパイルするような手順で

— ごめんなさいワカンナイ人多数かもm(..)m —

なので 旧型の設計資産(ソースコード)の大半が再利用可能と思われます。

【更に蛇足】

こうした「ハードウエア記述言語」ベースのIC設計データはIP(intellectual Property)資産と呼ばれ、有用な汎用品があり、BtoBですが一大市場を形成しています。

例えば戦闘機 F-35やグリペンに使われてる「PowerPC」は高機能でメカ制御に使いやすいCPUとして有名ですが、これをハードウエア記述言語で記述したIP(intellectual Property) はモトローラ社(現フリースケール)のベストセラーIPの一つです。

そしてARM社は、CPU設計「だけ」の会社ですが、ARM社の主力製品は「ARMプロセッサの設計ソースコード」なわけです。

PowerPCやARMは巨大なIPですがFPGAに書き込めばすぐCPUになります。こうしたIPはもっと小規模なものも広く流通していて、、、、まあ頑張れば数世代前のPCなら最新FPGAになら全部放り込めます。

なのでもしかすると、木霊さんご紹介の韓国軍艦、80286ベースコンピュータとか2代目玄武ミサイルなど韓国ならFPGAで修理とかやってるかも?(笑)

こんにちは。

・「冗長性」という言葉に騙されがちですが、二重化三重化は、故障率も二倍三倍になるんですよね。

同時にアップデートかけるなんてあまりにも馬鹿馬鹿しいヒューマンエラーは想定外でしょうけれど……両方とも自動アップデートが有効だった?そんなバカな……いや、しかし……

・影響を受けた銀行と、受けなかった銀行がありますよね。「全銀システム」なのになんで?って思いませんか?影響受けなかったところは、バックアップシステム持ってたのかな?

システムの多重化は手間も多重化しますからねぇ。

それを一気に交換しようというのがちょっとおかしな話のように思えます。

流石に何か事情があったのでしょうが……。

影響を受けなかった銀行の話も引用記事には書いてありましたが、ちょっと失念。